Recommonmark has been deprecated since 2021 [1] and the last release was

over 3 years ago [2]. As per their announcement, Markedly Structured

Text (MyST) Parser [3] is the recommended replacement.

For the most part, the existing documentation is compatible with MyST,

as both parsers are built around the CommonMark flavor of Markdown. The

main difference that affects coreboot is how the Sphinx toctree is

generated. Recommonmark has a feature called auto_toc_tree, which

converts single level lists of references into a toctree:

* [Part 1: Starting from scratch](part1.md)

* [Part 2: Submitting a patch to coreboot.org](part2.md)

* [Part 3: Writing unit tests](part3.md)

* [Managing local additions](managing_local_additions.md)

* [Flashing firmware](flashing_firmware/index.md)

MyST Parser does not provide a replacement for this feature, meaning the

toctree must be defined manually. This is done using MyST's syntax for

Sphinx directives:

```{toctree}

:maxdepth: 1

Part 1: Starting from scratch <part1.md>

Part 2: Submitting a patch to coreboot.org <part2.md>

Part 3: Writing unit tests <part3.md>

Managing local additions <managing_local_additions.md>

Flashing firmware <flashing_firmware/index.md>

```

Internally, auto_toc_tree essentially converts lists of references into

the Sphinx toctree structure that the MyST syntax above more directly

represents.

The toctrees were converted to the MyST syntax using the following

command and Python script:

`find ./ -iname "*.md" | xargs -n 1 python conv_toctree.py`

```

import re

import sys

in_list = False

f = open(sys.argv[1])

lines = f.readlines()

f.close()

with open(sys.argv[1], "w") as f:

for line in lines:

match = re.match(r"^[-*+] \[(.*)\]\((.*)\)$", line)

if match is not None:

if not in_list:

in_list = True

f.write("```{toctree}\n")

f.write(":maxdepth: 1\n\n")

f.write(match.group(1) + " <" + match.group(2) + ">\n")

else:

if in_list:

f.write("```\n")

f.write(line)

in_list = False

if in_list:

f.write("```\n")

```

While this does add a little more work for creating the toctree, this

does give more control over exactly what goes into the toctree. For

instance, lists of links to external resources currently end up in the

toctree, but we may want to limit it to pages within coreboot.

This change does break rendering and navigation of the documentation in

applications that can render Markdown, such as Okular, Gitiles, or the

GitHub mirror. Assuming the docs are mainly intended to be viewed after

being rendered to doc.coreboot.org, this is probably not an issue in

practice.

Another difference is that MyST natively supports Markdown tables,

whereas with Recommonmark, tables had to be written in embedded rST [4].

However, MyST also supports embedded rST, so the existing tables can be

easily converted as the syntax is nearly identical.

These were converted using

`find ./ -iname "*.md" | xargs -n 1 sed -i "s/eval_rst/{eval-rst}/"`

Makefile.sphinx and conf.py were regenerated from scratch by running

`sphinx-quickstart` using the updated version of Sphinx, which removes a

lot of old commented out boilerplate. Any relevant changes coreboot had

made on top of the previous autogenerated versions of these files were

ported over to the newly generated file.

From some initial testing the generated webpages appear and function

identically to the existing documentation built with Recommonmark.

TEST: `make -C util/docker docker-build-docs` builds the documentation

successfully and the generated output renders properly when viewed in

a web browser.

[1] https://github.com/readthedocs/recommonmark/issues/221

[2] https://pypi.org/project/recommonmark/

[3] https://myst-parser.readthedocs.io/en/latest/

[4] https://doc.coreboot.org/getting_started/writing_documentation.html

Change-Id: I0837c1722fa56d25c9441ea218e943d8f3d9b804

Signed-off-by: Nicholas Chin <nic.c3.14@gmail.com>

Reviewed-on: https://review.coreboot.org/c/coreboot/+/73158

Reviewed-by: Matt DeVillier <matt.devillier@gmail.com>

Tested-by: build bot (Jenkins) <no-reply@coreboot.org>

3.6 KiB

Intel DG43GT

This page describes how to run coreboot on the Intel DG43GT desktop.

Flashing coreboot

+---------------------+------------+

| Type | Value |

+=====================+============+

| Socketed flash | no |

+---------------------+------------+

| Model | W25X32 |

+---------------------+------------+

| Size | 4 MiB |

+---------------------+------------+

| In circuit flashing | NO! |

+---------------------+------------+

| Package | SOIC-8 |

+---------------------+------------+

| Write protection | No |

+---------------------+------------+

| Dual BIOS feature | No |

+---------------------+------------+

| Internal flashing | yes |

+---------------------+------------+

Internal programming

The SPI flash can be accessed internally using flashrom. Only the BIOS region can and needs to be written to.

$ flashrom -p internal --ifd -i bios -w coreboot.rom --noverify-all

External programming

ISP (in circuit programming) seems to be impossible on this board, which is a property it shares with many boards featuring the ICH10 southbridge. Recovering from a bad flash will require desoldering the flash! Desoldering the SPI flash can easily be done with a hot air station. Apply some flux around the SPI flash, set the hot air station to 350-400°C and after heating the chip up for a minute it should be possible to remove it.

Having removed the flash chip, you can reprogram it externally then resolder it using a soldering iron. Another option would be to hook up a SPI flash (socket) to the SPI header, for easier flash removing in the future (if you expect to be hacking on this board). To do this you first need to solder the SPI header to the board.

NOTE: This header cannot be used for ISP either.

NOTE2: Don't forget to connect the WP# and HOLD# pin on the SPI flash to 3.3V.

The layout of the header is:

+---+---+

GND <- | x | x | -> SPI_CLK

+---+---+

3VSB <- | x | x | -> SPI_MISO

+---+---+

| | x | -> SPI_MOSI

+---+---+

SPI_CS# <-| x | x | -> SPI_CS# (again)

+---+---+

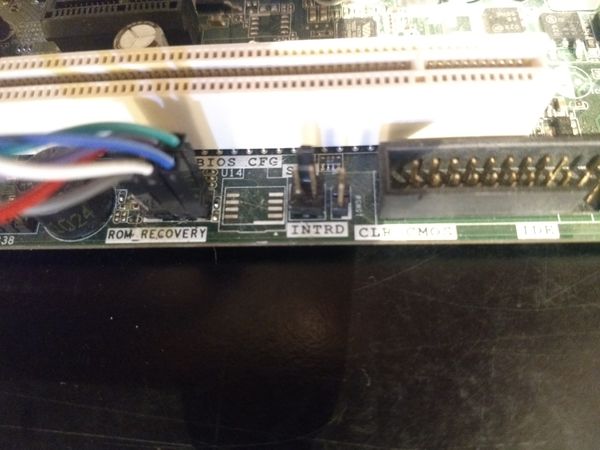

Picture of the board with the flash hooked on externally

Close up picture of the SPI flash pads and recovery header

Technology

+------------------+---------------------------------------------------+

| Northbridge | Intel G43 (called x4x in coreboot code) |

+------------------+---------------------------------------------------+

| Southbridge | Intel ICH10 (called i82801jx in coreboot code) |

+------------------+---------------------------------------------------+

| CPU (LGA775) | model f4x, f6x, 6fx, 1067x (pentium 4, d, core 2) |

+------------------+---------------------------------------------------+

| SuperIO | Winbond W83627DHG |

+------------------+---------------------------------------------------+

| Coprocessor | Intel ME (optionally enabled) |

+------------------+---------------------------------------------------+

| Clockgen (CK505) | SLG8XP549T |

+------------------+---------------------------------------------------+